## **Fundamentals of digital Systems**

ERMIT Departement, M. Bidnyi, Lecture synopsis, 2020

#### **Number Systems**

#### **Roman Numerals**

The Romans devised a system that was a substantial improvement over hash marks, because it used a variety of symbols (or *ciphers*) to represent increasingly large quantities.

The notation for 1 is the capital letter I. The notation for 5 is the capital letter V. Other ciphers possess increasing values:

X = 10 L = 50 C = 100 D = 500M = 1000

If a cipher is accompanied by another cipher of equal or lesser value to the immediate right of it, with no ciphers greater than that other cipher to the right of that other cipher, that other cipher's value is added to the total quantity.

Thus, VIII symbolizes the number 8, and CLVII symbolizes the number 157. On the other hand, if a cipher is accompanied by another cipher of lesser value to the immediate left, that other cipher's value is *subtracted* from the first. Therefore, IV symbolizes the number 4 (V minus I), and CM symbolizes the number 900 (M minus C).

You might have noticed that ending credit sequences for most motion pictures contain a notice for the date of production, in Roman numerals. For the year 1987, it would read: MCMLXXXVII. Let's break this numeral down into its constituent parts, from left to right:

M = 1000 + CM = 900 + L = 50 + XXX = 30 + V = 5 + II = 2

Aren't you glad we don't use this system of numeration? Large numbers are very difficult to denote this way, and the left vs. right / subtraction vs. addition of values can be very confusing, too.

Another major problem with this system is that there is no provision for representing the number zero or negative numbers, both very important concepts in mathematics.

Roman culture, however, was more pragmatic with respect to mathematics than most, choosing only to develop their numeration system as far as it was necessary for use in daily life.

## **Place Value**

We owe one of the most important ideas in numeration to the ancient Babylonians, who were the first (as far as we know) to develop the concept of cipher position, or place value, in representing larger numbers.

Instead of inventing new ciphers to represent larger numbers, as the Romans did, they re-used the same ciphers, placing them in different positions from right to left.

Our own decimal numeration system uses this concept, with only ten ciphers (0, 1, 2, 3, 4, 5, 6, 7, 8, and 9) used in "weighted" positions to represent very large and very small numbers.

Each cipher represents an integer quantity, and each place from right to left in the notation represents a multiplying constant, or *weight*, for each integer quantity.

For example, if we see the decimal notation "1206", we known that this may be broken down into its constituent weight-products as such: 1206 = 1000 + 200 + 6 $1206 = (1 \times 1000) + (2 \times 100) + (0 \times 10) + (6 \times 1)$

Each cipher is called a *digit* in the decimal numeration system, and each weight, or place value, is ten times that of the one to the immediate right.

So, we have a *ones* place, a tens place, a *hundreds* place, a thousands place, and so on, working from right to left.

Right about now, you're probably wondering why I'm laboring to describe the obvious. Who needs to be told how decimal numeration works, after you've studied math as advanced as algebra and trigonometry?

The reason is to better understand other numeration systems, by first knowing the how's and why's of the one you're already used to.

The decimal numeration system uses ten ciphers, and place-weights that are multiples of ten. What if we made a numeration system with the same strategy of weighted places, except with fewer or more ciphers?

## **Binary Numeration**

The binary numeration system is such a system. Instead of ten different cipher symbols, with each weight constant being ten times the one before it, we only have *two* cipher symbols, and each weight constant is *twice* as much as the one before it.

The two allowable cipher symbols for the binary system of numeration are "1" and "0," and these ciphers are arranged right-to-left in doubling values of weight. The rightmost place is the *ones* place, just as with decimal notation. Proceeding to the left, we have the *twos* place, the *fours* place, the *eights* place, the *sixteens* place, and so on.

For example, the following binary number can be expressed, just like the decimal number 1206, as a sum of each cipher value times its respective weight constant:

11010 = 2 + 8 + 16 = 26

11010 = (1 x 16) + (1 x 8) + (0 x 4) + (1 x 2) + (0 x 1)

This can get quite confusing, as I've written a number with binary numeration (11010), and then shown its place values and total in standard, decimal numeration form (16 + 8 + 2 = 26). In the above example, we're mixing two different kinds of numerical notation.

To avoid unnecessary confusion, we have to denote which form of numeration we're using when we write (or type!). Typically, this is done in subscript form, with a "2" for binary and a "10" for decimal, so the binary number  $11010_2$  is equal to the decimal number  $26_{10}$ .

The subscripts are not mathematical operation symbols like superscripts (exponents) are. All they do is indicate what system of numeration we're using when we write these symbols for other people to read. If you see " $3_{10}$ ", all this means is the number three written using *decimal* numeration.

However, if you see " $3^{10}$ ,", this means something completely different: three to the tenth power (59,049). As usual, if no subscript is shown, the cipher(s) are assumed to be representing a decimal number.

Commonly, the number of cipher types (and therefore, the place-value multiplier) used in a numeration system is called that system's base. Binary is referred to as "base two" numeration, and decimal as "base ten."

Additionally, we refer to each cipher position in binary as a *bit* rather than the familiar word *digit* used in the decimal system.

Now, why would anyone use binary numeration? The decimal system, with its ten ciphers, makes a lot of sense, being that we have ten fingers on which to count between our two hands. (It is interesting that some ancient central American cultures used numeration systems with a base of twenty.

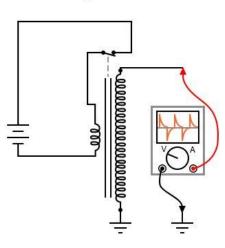

Presumably, they used both fingers and toes to count!!). But the primary reason that the binary numeration system is used in modern electronic computers is because of the ease of representing two cipher states (0 and 1) electronically.

With relatively simple circuitry, we can perform mathematical operations on binary numbers by representing each bit of the numbers by a circuit which is either on (current) or off (no current). Just like the abacus with each rod representing another decimal digit, we simply add more circuits to give us more bits to symbolize larger numbers.

Binary numeration also lends itself well to the storage and retrieval of numerical information: on magnetic tape (spots of iron oxide on the tape either being magnetized for a binary "1" or demagnetized for a binary "0"), optical disks (a laserburned pit in the aluminum foil representing a binary "1" and an unburned spot representing a binary "0"), or a variety of other media types.

Before we go on to learning exactly how all this is done in digital circuitry, we need to become more familiar with binary and other associated systems of numeration.

## **Decimal versus Binary Numeration**

Let's count from zero to twenty using four <u>different kinds of numeration</u> <u>systems</u>: hash marks, Roman numerals, decimal, and binary:

| System:   | Hash Marks              | Roman | Decimal | Binar |

|-----------|-------------------------|-------|---------|-------|

| Zero      | n/a                     | n/a   | 0       | 0     |

| One       | 1                       | 1     | 1       | 1     |

| Two       | Ш                       | 11    | 2       | 10    |

| Three     | Ш                       | Ш     | 3       | 11    |

| Four      | 1111                    | IV    | 4       | 100   |

| Five      | /111/                   | V     | 5       | 101   |

| Six       | /111/1                  | VI    | 6       | 110   |

| Seven     | /111/ 11                | VII   | 7       | 111   |

| Eight     | /111/ 111               | VIII  | 8       | 1000  |

| Nine      | /111/ 1111              | IX    | 9       | 1001  |

| Ten       | /111/ /111/             | Х     | 10      | 1010  |

| Eleven    | /111/ /111/ 1           | XI    | 11      | 1011  |

| Twelve    | /111/ /111/ 11          | XII   | 12      | 1100  |

| Thirteen  | /111/ /111/ 111         | XIII  | 13      | 1101  |

| Fourteen  | /111/ /111/ 1111        | XIV   | 14      | 1110  |

| Fifteen   | /111/ /111/ /111/       | XV    | 15      | 1111  |

| Sixteen   | /111/ /111/ /111/ 1     | XVI   | 16      | 10000 |

| Seventeen | /11/ /11/ /11/ 11       | XVII  | 17      | 10001 |

| Eighteen  | /11/ /11/ /11/ 11       | XVIII | 18      | 10010 |

| Nineteen  | /11/ /11/ /11/ 111      | XIX   | 19      | 10011 |

| Twenty    | /111/ /111/ /111/ /111/ | XX    | 20      | 10100 |

Neither hash marks nor the Roman system are very practical for symbolizing large numbers. Obviously, place-weighted systems such as decimal and binary are more efficient for the task.

Notice, though, how much shorter decimal notation is over binary notation, for the same number of quantities. What takes five bits in binary notation only takes two digits in decimal notation.

This raises an interesting question regarding different numeration systems: how large of a number can be represented with a limited number of cipher positions, or places? With the crude hash-mark system, the number of places IS the largest number that can be represented, since one hash mark "place" is required for every integer step.

For place-weighted systems of numeration, however, the answer is found by taking base of the numeration system (10 for decimal, 2 for binary) and raising it to the power of the number of places.

For example, 5 digits in a decimal numeration system can represent 100,000 different integer number values, from 0 to 99,999 (10 to the 5th power = 100,000). 8 bits in a binary numeration system can represent 256 different integer number values, from 0 to 11111111 (binary), or 0 to 255 (decimal), because 2 to the 8th power equals 256.

With each additional place position to the number field, the capacity for representing numbers increases by a factor of the base (10 for decimal, 2 for binary).

An interesting footnote for this topic is the one of the first electronic digital computers, the Eniac.

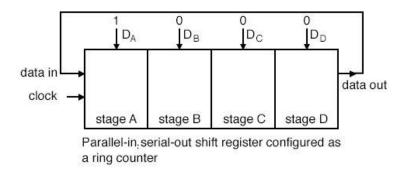

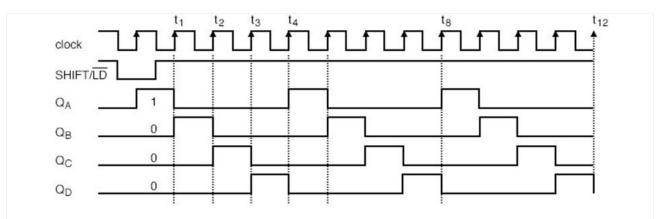

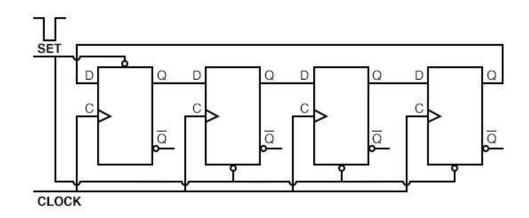

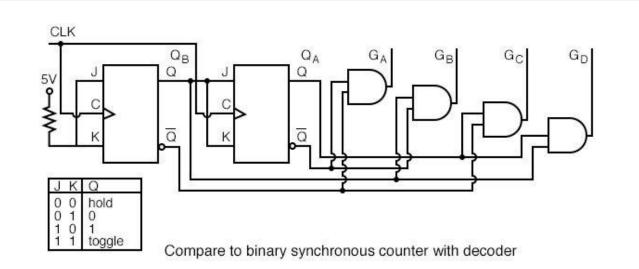

The designers of the Eniac chose to represent numbers in decimal form, digitally, using a series of circuits called "ring counters" instead of just going with the binary numeration system, in an effort to minimize the number of circuits required to represent and calculate very large numbers.

This approach turned out to be counter-productive, and virtually all digital computers since then have been purely binary in design.

## **Binary to Decimal Conversion**

To convert a number in binary numeration to its equivalent in decimal form, all you have to do is calculate the sum of all the products of bits with their respective place-weight constants. To illustrate:

The bit on the far right side is called the Least Significant Bit (LSB), because it stands in the place of the lowest weight (the one's place).

The bit on the far left side is called the Most Significant Bit (MSB), because it stands in the place of the highest weight (the one hundred twenty-eight's place).

Remember, a bit value of "1" means that the respective place weight gets added to the total value, and a bit value of "0" means that the respective place weight does *not* get added to the total value. With the above example, we have:

$128_{10} + 64_{10} + 8_{10} + 4_{10} + 1_{10} = 205_{10}$

If we encounter a binary number with a dot (.), called a "binary point" instead of a decimal point, we follow the same procedure, realizing that each place weight to the right of the point is one-half the value of the one to the left of it (just as each place weight to the right of a *decimal* point is one-tenth the weight of the one to the left of it). For example:

$4_{10} + 1_{10} + 0.25_{10} + 0.125_{10} = 5.375_{10}$

#### **Octal and Hexadecimal to Decimal Conversion**

Although the prime intent of octal and hexadecimal numeration systems is for the "shorthand" representation of binary numbers in digital electronics, we sometimes have the need to convert from either of those systems to decimal form.

Of course, we could simply convert the hexadecimal or octal format to binary, then convert from binary to decimal, since we already know how to do both, but we can also convert directly.

Because octal is a base-eight numeration system, each place-weight value differs from either adjacent place by a factor of eight.

For example, the octal number 245.37 can be broken down into place values as such:

The decimal value of each octal place-weight times its respective cipher multiplier can be determined as follows:

$(2 \times 64_{10}) + (4 \times 8_{10}) + (5 \times 1_{10}) + (3 \times 0.125_{10}) + (7 \times 0.015625_{10}) = 165.484375_{10}$

## **Hexadecimal to Decimal Conversion**

The technique for converting hexadecimal notation to decimal is the same, except that each successive place-weight changes by a factor of sixteen.

Simply denote each digit's weight, multiply each hexadecimal digit value by its respective weight (in decimal form), then add up all the decimal values to get a total.

For example, the hexadecimal number  $30F.A9_{16}$  can be converted like this:

Hexadecimal Digits = <u>3</u> 0 F . A 9 . <u>A</u> 9 .

$(3 \times 256_{10}) + (0 \times 16_{10}) + (15 \times 1_{10}) + (10 \times 0625_{10}) + (9 \times 0.00390625_{10}) = 783.66015625_{10}$

These basic techniques may be used to convert a numerical notation of any base into decimal form, if you know the value of that numeration system's base.

#### **Conversion From Decimal Numeration**

Because <u>octal and hexadecimal numeration</u> systems have bases that are multiples of binary (base 2), conversion back and forth between either hexadecimal or octal and binary is very easy.

Also, because we are so familiar with the decimal system, converting binary, octal, or hexadecimal to decimal form is relatively easy (simply add up the products of cipher values and place-weights).

However, conversion from decimal to any of these "strange" numeration systems is a different matter.

#### **Trial-and-Fit Method**

The method which will probably make the most sense is the "trial-and-fit" method, where you try to "fit" the binary, octal, or hexadecimal notation to the desired value as represented in decimal form.

For example, let's say that I wanted to represent the decimal value of 87 in binary form. Let's start by drawing a binary number field, complete with placeweight values: Well, we know that we won't have a "1" bit in the 128's place, because that would immediately give us a value greater than 87.

However, since the next weight to the right (64) is less than 87, we know that we must have a "1" there.

. 1 . \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ Decimal value so far = 64 10 Weight = 64 32 16 8 4 2 1 (in decimal notation)

If we were to make the next place to the right a "1" as well, our total value would be  $64_{10} + 32_{10}$ , or  $96_{10}$ . This is greater than  $87_{10}$ , so we know that this bit must be a "0".

If we make the next (16's) place bit equal to "1," this brings our total value to  $64_{10} + 16_{10}$ , or  $80_{10}$ , which is closer to our desired value ( $87_{10}$ ) without exceeding it:

. 1 0 1 . - - - - - - Decimal value so far = 80<sub>10</sub> Weight = 64 32 16 8 4 2 1 (in decimal notation)

By continuing in this progression, setting each lesser-weight bit as we need to come up to our desired total value without exceeding it, we will eventually arrive at the correct figure:

Decimal value so far = 8710

## **Trial-and-Fit Method in Octal and Hexadecimal**

This trial-and-fit strategy will work with octal and hexadecimal conversions, too. Let's take the same decimal figure,  $87_{10}^{-}$ , and convert it to octal numeration:

If we put a cipher of "1" in the 64's place, we would have a total value of  $64_{10}$  (less than  $87_{10}$ ). If we put a cipher of "2" in the 64's place, we would have a total value of  $128_{10}$  (greater than  $87_{10}$ ). This tells us that our octal numeration must start with a "1" in the 64's place:

$\begin{array}{cccccccc} \cdot & 1 & & \\ \cdot & & - & - & - & \text{Decimal value so far} = 64_{10} \\ \text{Weight} = & 64_{10} & & \\ \text{(in decimal notation)} \end{array}$

Now, we need to experiment with cipher values in the 8's place to try and get a total (decimal) value as close to 87 as possible without exceeding it. Trying the first few cipher options, we get:

For "1" we have:  $64_{10} + 8_{10} = 72_{10}$ For "2" we have:  $64_{10} + 16_{10} = 80_{10}$ For "3" we have:  $64_{10} + 24_{10} = 88_{10}$

#### **Logic Gates**

#### **Boolean Arithmetic**

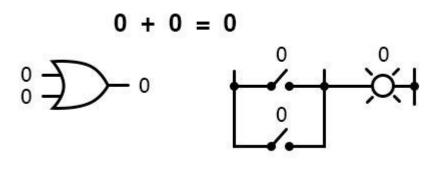

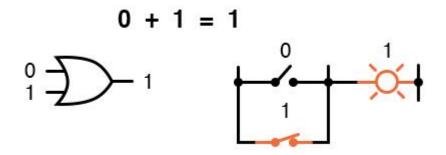

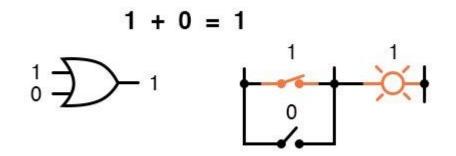

Let us begin our exploration of Boolean algebra by adding numbers together:

0 + 0 = 0 0 + 1 = 1 1 + 0 = 11 + 1 = 1

The first three sums make perfect sense to anyone familiar with elementary addition.

The last sum, though, is quite possibly responsible for more confusion than any other single statement in digital electronics, because it seems to run contrary to the basic principles of mathematics.

Well, it does contradict the principles of addition for real numbers, but not for Boolean numbers.

Remember that in the world of Boolean algebra, there are only two possible values for any quantity and for any arithmetic operation: 1 or 0.

There is no such thing as "2" within the scope of Boolean values. Since the sum "1 + 1" certainly isn't 0, it must be 1 by process of elimination.

It does not matter how many or few terms we add together, either. Consider the following sums:

0 + 1 + 1 = 1 1 + 1 + 1 = 1 0 + 1 + 1 + 1 = 11 + 0 + 1 + 1 + 1 = 1

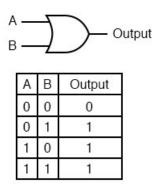

## **OR** Gate

Take a close look at the two-term sums in the first set of equations.

Does that pattern look familiar to you? It should! It is the same pattern of 1's and 0's as seen in the truth table for an <u>OR gate</u>.

In other words, Boolean addition corresponds to the logical function of an "OR" gate, as well as to parallel switch contacts:

1 + 1 = 1 1 + 1 = 1 1 + 1 = 1 1 + 1 + 1 1 + 1 + 1

There is no such thing as subtraction in the realm of Boolean mathematics.

Subtraction implies the existence of negative numbers: 5 - 3 is the same thing as 5 + (-3), and in Boolean algebra negative quantities are forbidden.

There is no such thing as division in Boolean mathematics, either, since division is really nothing more than *compounded subtraction*, in the same way that multiplication is *compounded addition*.

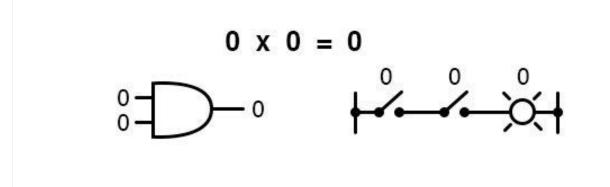

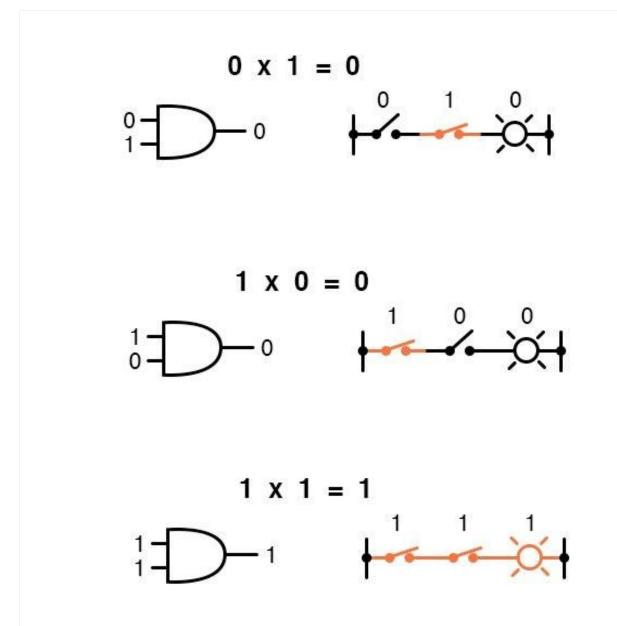

#### **AND Gate**

Multiplication is valid in Boolean algebra, and thankfully it is the same as in real-number algebra: anything multiplied by  $\mathbf{0}$  is  $\mathbf{0}$ , and anything multiplied by  $\mathbf{1}$  remains unchanged:

0 x 0 = 0 0 x 1 = 0 1 x 0 = 0 1 x 1 = 1

This set of equations should also look familiar to you: it is the same pattern found in the truth table for an <u>AND gate</u>.

In other words, Boolean multiplication corresponds to the logical function of an "AND" gate, as well as to series switch contacts:

Like "normal" algebra, Boolean algebra uses alphabetical letters to denote variables.

Unlike "normal" algebra, though, Boolean variables are always CAPITAL letters, never lower-case.

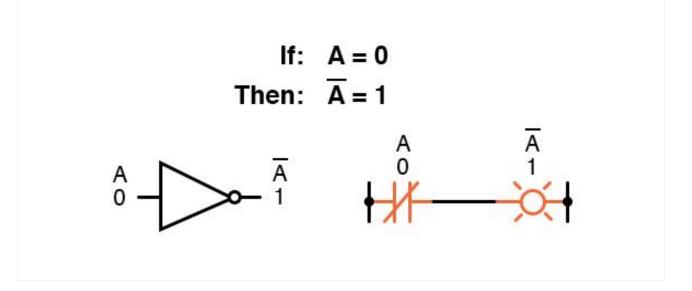

Because they are allowed to possess only one of two possible values, either 1 or 0, each and every variable has a *complement*: the opposite of its value.

For example, if variable "A" has a value of  $\mathbf{0}$ , then the complement of A has a value of  $\mathbf{1}$ .

Boolean notation uses a bar above the variable character to denote complementation, like this:

If:

$$A = 0$$

Then:  $\overline{A} = 1$

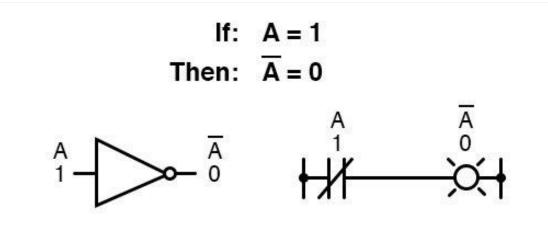

If:  $A = 1$

Then:  $\overline{A} = 0$

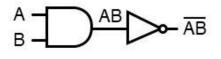

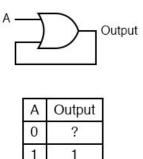

## **NOT Gate**

In written form, the complement of "**A**" denoted as "**A-not**" or "**A-bar**". Sometimes a "prime" symbol is used to represent complementation.

For example, **A**' would be the complement of **A**, much the same as using a prime symbol to denote differentiation in calculus rather than the fractional notation d/dt.

Usually, though, the "bar" symbol finds more widespread use than the "*prime*" symbol, for reasons that will become more apparent later in this chapter.

Boolean complementation finds equivalency in the form of the **NOT gate**, or a normally-closed switch or relay contact:

The basic definition of Boolean quantities has led to the simple rules of addition and multiplication, and has excluded both subtraction and division as valid arithmetic operations.

We have a symbology for denoting Boolean variables, and their complements. In the next section we will proceed to develop Boolean identities.

## **REVIEW:**

• Boolean addition is equivalent to the <u>OR</u> logic function, as well as parallel switch contacts.

• Boolean multiplication is equivalent to the *AND* logic function, as well as series switch contacts.

• Boolean complementation is equivalent to the <u>NOT</u> logic function, as well as *normally-closed* relay contacts.

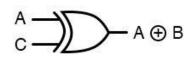

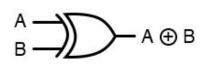

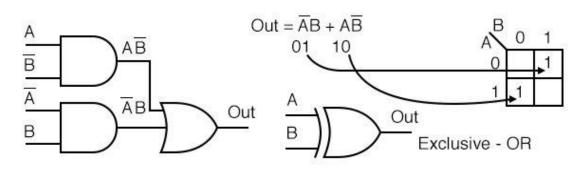

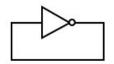

## The Exclusive-OR Function: The XOR Gate

One element conspicuously missing from the set of Boolean operations is that of Exclusive-OR, often represented as XOR.

Whereas the OR function is equivalent to Boolean addition, the AND function to Boolean multiplication, and the NOT function (inverter) to Boolean complementation, there is no direct Boolean equivalent for Exclusive-OR.

This hasn't stopped people from developing a symbol to represent this logic gate, though:

This logic gate symbol is seldom used in <u>Boolean expressions</u> because the identities, laws, and rules of simplification involving addition, multiplication, and complementation do not apply to it.

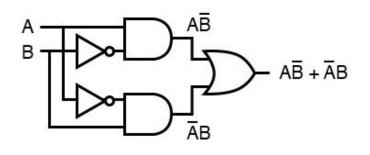

However, there is a way to represent the Exclusive-OR function in terms of OR and AND, as has been shown in previous chapters: AB' + A'B

... is equivalent to ...

$A \oplus B = A\overline{B} + \overline{A}B$

As a Boolean equivalency, this rule may be helpful in simplifying some Boolean expressions.

Any expression following the AB' + A'B form (two AND gates and an OR gate) may be replaced by a single Exclusive-OR gate.

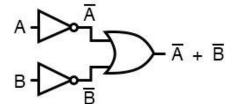

## **DeMorgan's Theorems**

A mathematician named DeMorgan developed a pair of important rules regarding group complementation in Boolean algebra.

Group complementation is to the complement of a group of terms, represented by a long bar over more than one variable.

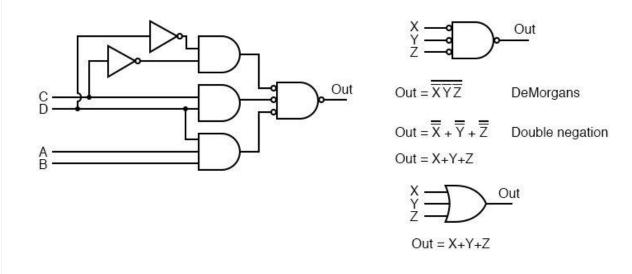

Logic gates that inverting all inputs to a gate reverses that gate's essential function from AND to OR, or vice versa, and also inverts the output.

So, an OR gate with all inputs inverted (a Negative-OR gate) behaves the same as a NAND gate, and an AND gate with all inputs inverted (a Negative-AND gate) behaves the same as a NOR gate.

DeMorgan's theorems state the same equivalence in "backward" form: that inverting the output of any gate results in the same function as the opposite type of gate (AND vs. OR) with inverted inputs:

... is equivalent to ...

$\overline{AB} = \overline{A} + \overline{B}$

A long bar extending over the term AB acts as a grouping symbol, and as such is entirely different from the product of A and B independently inverted.

In other words, (AB)' is not equal to A'B'. Because the "prime" symbol (') cannot be stretched over two variables like a bar can, we are forced to use parentheses to make it apply to the whole term AB in the previous sentence.

A bar, however, acts as its own grouping symbol when stretched over more than one variable.

This has profound impact on how Boolean expressions are evaluated and reduced, as we shall see.

#### **DeMorgan's Theorem**

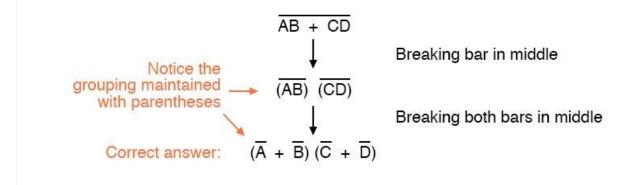

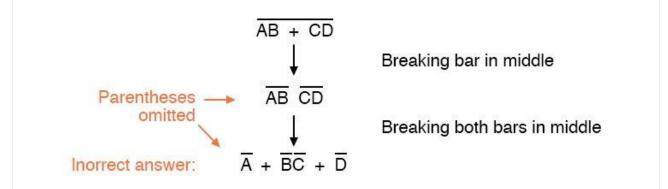

DeMorgan's theorem may be thought of in terms of breaking a long bar symbol.

When a long bar is broken, the operation directly underneath the break changes from addition to multiplication, or vice versa, and the broken bar pieces remain over the individual variables. To illustrate:

DeMorgan's Theorems Break!  $\overrightarrow{AB}$   $\overrightarrow{AB}$   $\overrightarrow{A}$  + B NAND to Negative-OR  $\overrightarrow{B}$  Heorems  $\overrightarrow{A}$  + B  $\overrightarrow{A}$  + B  $\overrightarrow{A}$  + B  $\overrightarrow{A}$  + B NOR to Negative-AND

When multiple "layers" of bars exist in an expression, you may only break one bar at a time, and it is generally easier to begin simplification by breaking the longest (uppermost) bar first.

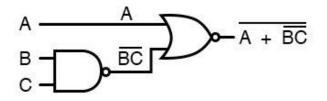

To illustrate, let's take the expression (A + (BC)')' and reduce it using DeMorgan's Theorems:

Following the advice of breaking the longest (uppermost) bar first, we'll begin by breaking the bar covering the entire expression as a first step:

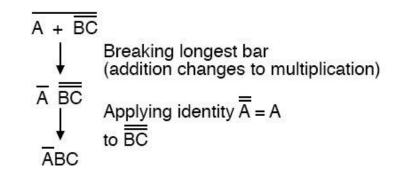

As a result, the original circuit is reduced to a three-input AND gate with the A input inverted:

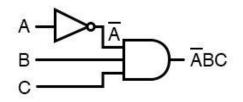

You should never break more than one bar in a single step, as illustrated here:

As tempting as it may be to conserve steps and break more than one bar at a time, it often leads to an incorrect result, so don't do it!

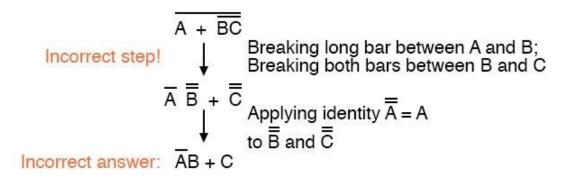

It is possible to properly reduce this expression by breaking the short bar first, rather than the long bar first:

The end result is the same, but more steps are required compared to using the first method, where the longest bar was broken first.

Note how in the third step we broke the long bar in two places.

This is a legitimate mathematical operation, and not the same as breaking two bars in one step!

The prohibition against breaking more than one bar in one step is not a prohibition against breaking a bar in more than one place.

Breaking in more than one place in a single step is okay; breaking more than one bar in a single step is not.

You might be wondering why parentheses were placed around the subexpression B' + C', considering the fact that I just removed them in the next step.

This is done to emphasize an important but easily neglected aspect of DeMorgan's theorem.

Since a long bar functions as a grouping symbol, the variables formerly grouped by a broken bar must remain grouped lest proper precedence (order of operation) be lost.

In this example, it really wouldn't matter if I forgot to put parentheses in after breaking the short bar, but in other cases it might.

Consider this example, starting with a different expression:

As you can see, maintaining the grouping implied by the complementation bars for this expression is crucial to obtaining the correct answer.

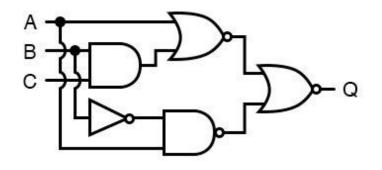

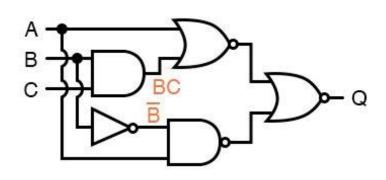

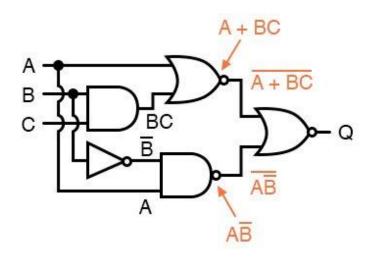

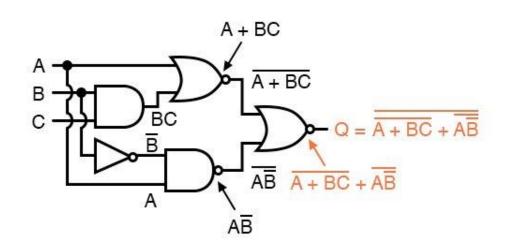

Let's apply the principles of DeMorgan's theorems to the simplification of a gate circuit:

As always, our first step in simplifying this circuit must be to generate an equivalent Boolean expression.

We can do this by placing a sub-expression label at the output of each gate, as the inputs become known. Here's the first step in this process:

Next, we can label the outputs of the first NOR gate and the NAND gate.

When dealing with inverted-output gates it easier to write an expression for the gate's output without the final inversion, with an arrow pointing to just before the inversion bubble.

Then, at the wire leading out of the gate (after the bubble), I write the full, complemented expression.

This helps ensure I don't forget a complementing bar in the sub-expression, by forcing myself to split the expression-writing task into two steps:

Finally, we write an expression (or pair of expressions) for the last NOR gate:

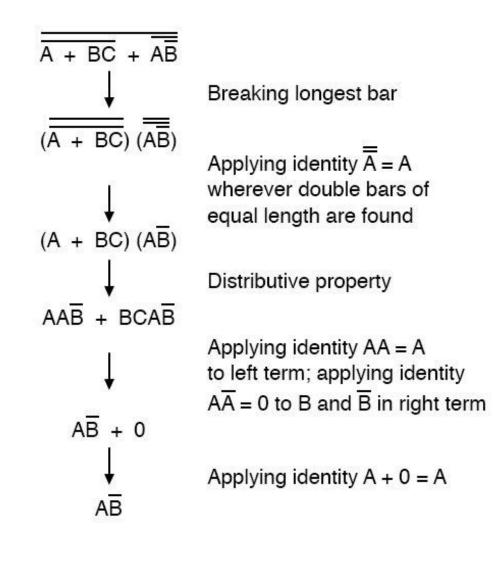

Now, we reduce this expression using the identities, properties, rules, and theorems (DeMorgan's) of Boolean algebra:

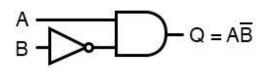

The equivalent gate circuit for this much-simplified expression is as follows:

## **REVIEW:**

- DeMorgan's Theorems describe the equivalence between gates with inverted inputs and gates with inverted outputs. Simply put, a NAND gate is equivalent to a Negative-OR gate, and a NOR gate is equivalent to a Negative-AND gate.

- When "breaking" a complementation bar in a Boolean expression, the operation directly underneath the break (addition or multiplication) reverses, and the broken bar pieces remain over the respective terms.

- It is often easier to approach a problem by breaking the longest (uppermost) bar before breaking any bars under it. You must never attempt to break two bars in one step!

- Complementation bars function as grouping symbols. Therefore, when a bar is broken, the terms underneath it must remain grouped. Parentheses may be placed around these grouped terms as a help to avoid changing precedence.

## **Converting Truth Tables into Boolean Expressions**

In designing digital circuits, the designer often begins with a truth table describing what the circuit should do.

The design task is largely to determine what type of circuit will perform the function described in the truth table.

While some people seem to have a natural ability to look at a truth table and immediately envision the necessary logic gate or relay logic circuitry for the task, there are procedural techniques available for the rest of us.

Here, Boolean algebra proves its utility in a most dramatic way.

To illustrate this procedural method, we should begin with a realistic design problem.

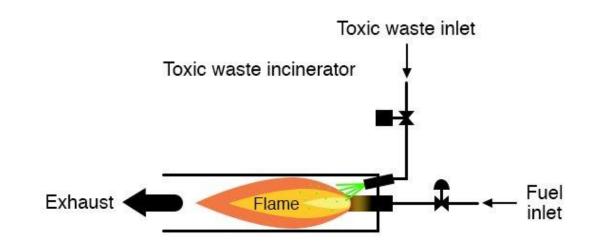

Suppose we were given the task of designing a flame detection circuit for a toxic waste incinerator.

The intense heat of the fire is intended to neutralize the toxicity of the waste introduced into the incinerator.

Such combustion-based techniques are commonly used to neutralize medical waste, which may be infected with deadly viruses or bacteria:

So long as a flame is maintained in the incinerator, it is safe to inject waste into it to be neutralized.

If the flame were to be extinguished, however, it would be unsafe to continue to inject waste into the combustion chamber, as it would exit the exhaust unneutralized, and pose a health threat to anyone in close proximity to the exhaust. What we need in this system is a sure way of detecting the presence of a flame, and permitting waste to be injected only if a flame is "proven" by the flame detection system.

Several different flame-detection technologies exist: optical (detection of light), thermal (detection of high temperature), and electrical conduction (detection of ionized particles in the flame path), each one with its unique advantages and disadvantages.

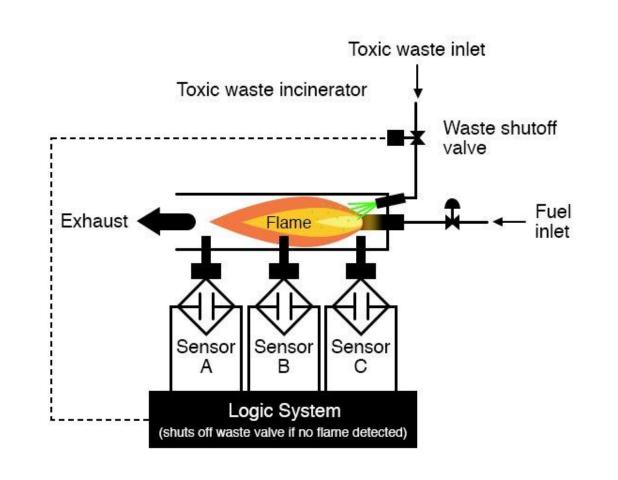

Suppose that due to the high degree of hazard involved with potentially passing un-neutralized waste out the exhaust of this incinerator, it is decided that the flame detection system be made redundant (multiple sensors), so that failure of a single sensor does not lead to an emission of toxins out the exhaust.

Each sensor comes equipped with a normally-open contact (open if no flame, closed if flame detected) which we will use to activate the inputs of a logic system:

Our task, now, is to design the circuitry of the logic system to open the waste valve if and only if there is good flame proven by the sensors.

First, though, we must decide what the logical behavior of this control system should be.

Do we want the valve to be opened if only one out of the three sensors detects flame? Probably not, because this would defeat the purpose of having multiple sensors.

If any one of the sensors were to fail in such a way as to falsely indicate the presence of flame when there was none, a logic system based on the principle of "any one out of three sensors showing flame" would give the same output that a single-sensor system would with the same failure.

A far better solution would be to design the system so that the valve is commanded to open if and only if *all three sensors* detect a good flame.

This way, any single, failed sensor falsely showing flame could not keep the valve in the open position; rather, it would require all three sensors to be failed in the same manner—a highly improbable scenario—for this dangerous condition to occur.

Thus, our truth table would look like this:

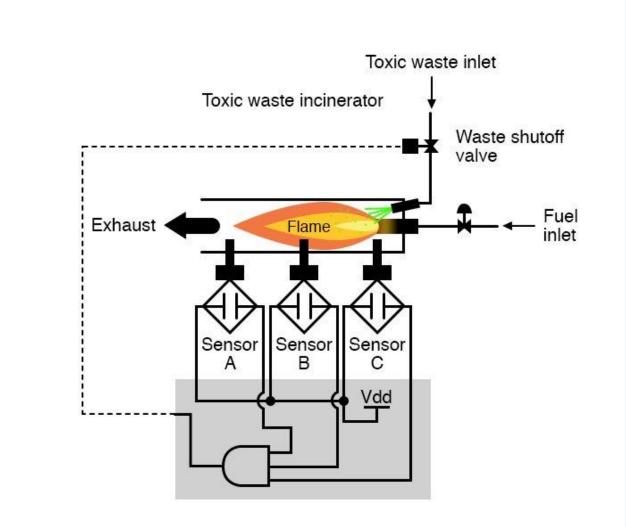

It does not require much insight to realize that this functionality could be generated with a three-input AND gate: the output of the circuit will be "high" if and only if input A *AND* input B *AND* input C are all "high:"

If using relay circuitry, we could create this AND function by wiring three relay contacts in series, or simply by wiring the three sensor contacts in series, so that the only way electrical power could be sent to open the waste valve is if all three sensors indicate flame:

While this design strategy maximizes safety, it makes the system very susceptible to sensor failures of the opposite kind.

Suppose that one of the three sensors were to fail in such a way that it indicated no flame when there really was a good flame in the incinerator's combustion chamber.

That single failure would shut off the waste valve unnecessarily, resulting in lost production time and wasted fuel (feeding a fire that wasn't being used to incinerate waste).

It would be nice to have a logic system that allowed for this kind of failure without shutting the system down unnecessarily, yet still provide sensor redundancy so as to maintain safety in the event that any single sensor failed "high" (showing flame at all times, whether or not there was one to detect).

A strategy that would meet both needs would be a "two out of three" sensor logic, whereby the waste valve is opened if at least two out of the three sensors show good flame.

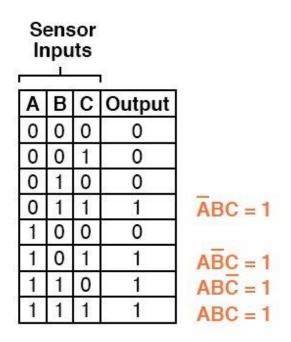

The truth table for such a system would look like this:

| Α | В | С | Output |               |

|---|---|---|--------|---------------|

| 0 | 0 | 0 | 0      | Output = 0    |

| 0 | 0 | 1 | 0      | (close valve) |

| 0 | 1 | 0 | 0      |               |

| 0 | 1 | 1 | 1      |               |

| 1 | 0 | 0 | 0      |               |

| 1 | 0 | 1 | 1      |               |

| 1 | 1 | 0 | 1      | Output = 1    |

| 1 | 1 | 1 | 1      | (open valve)  |

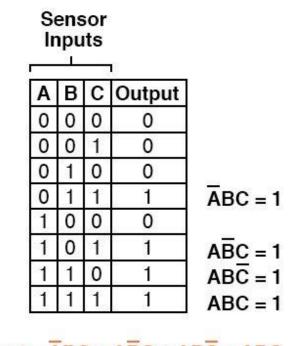

**Using Sum-Of-Products**

Here, it is not necessarily obvious what kind of logic circuit would satisfy the truth table.

However, a simple method for designing such a circuit is found in a standard form of Boolean expression called the *Sum-Of-Products*, or *SOP*, form.

As you might suspect, a Sum-Of-Products Boolean expression is literally a set of Boolean terms added (*summed*) together, each term being a multiplicative (*product*) combination of Boolean variables.

An example of an SOP expression would be something like this: ABC + BC + DF, the sum of products "ABC," "BC," and "DF."

Sum-Of-Products expressions are easy to generate from truth tables.

All we have to do is examine the truth table for any rows where the output is "high" (1), and write a Boolean product term that would equal a value of 1 given those input conditions.

For instance, in the fourth row down in the truth table for our two-out-of-three logic system, where A=0, B=1, and C=1, the product term would be A'BC, since that term would have a value of 1 if and only if A=0, B=1, and C=1 (it is minterm):

| Α | В | С | Output | 8.<br>8 |    |

|---|---|---|--------|---------|----|

| 0 | 0 | 0 | 0      | 8       |    |

| 0 | 0 | 1 | 0      | 3       |    |

| 0 | 1 | 0 | 0      |         |    |

| 0 | 1 | 1 | 1      | 7       | ĀB |

| 1 | 0 | 0 | 0      | 55<br>  |    |

| 1 | 0 | 1 | 1      | 8<br>0  |    |

| 1 | 1 | 0 | 11     | a<br>a  |    |

| 1 | 1 | 1 | 1      | 8       |    |

Three other rows of the truth table have an output value of 1, so those rows also need Boolean product expressions to represent them:

Finally, we join these four Boolean product expressions together by addition, to create a single Boolean expression describing the truth table as a whole:

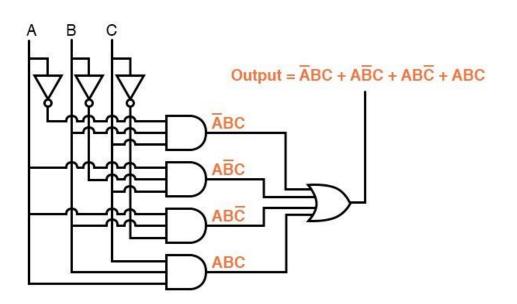

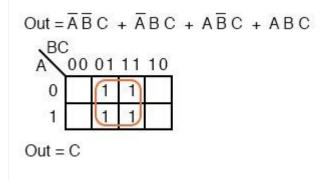

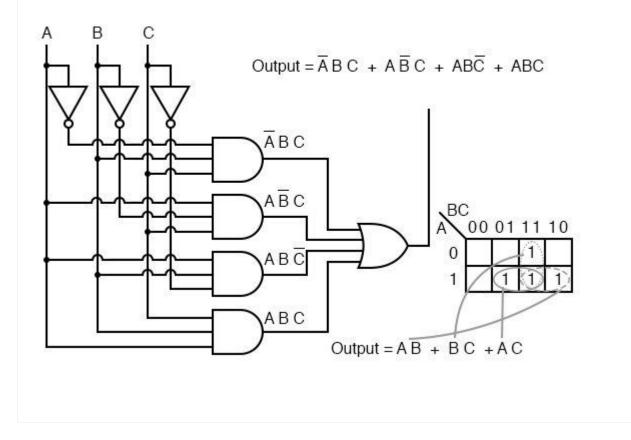

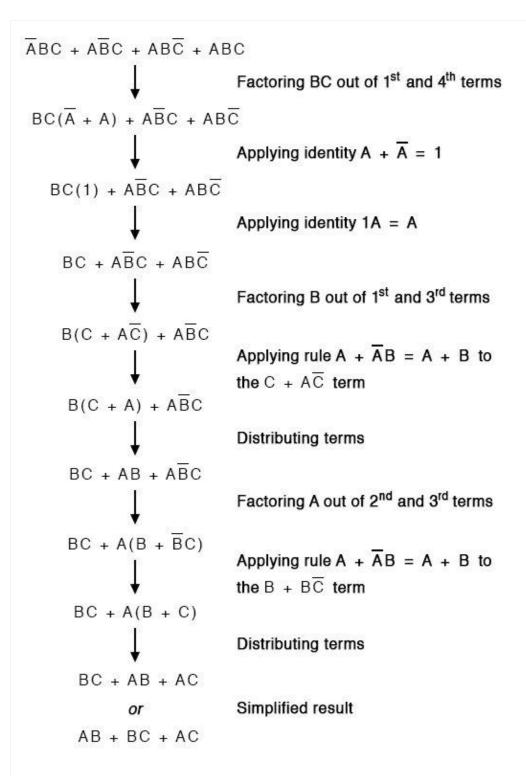

# $Output = \overline{A}BC + A\overline{B}C + AB\overline{C} + ABC$

Now that we have a Boolean Sum-Of-Products expression for the truth table's function, we can easily design a logic gates circuit based on that expression:

Unfortunately, this circuit is quite complex, and could benefit from simplification.

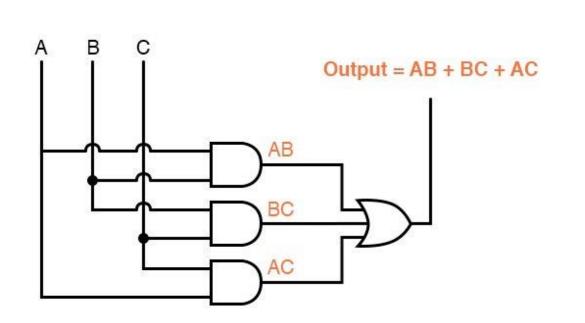

Using Boolean algebra techniques, the expression may be significantly simplified:

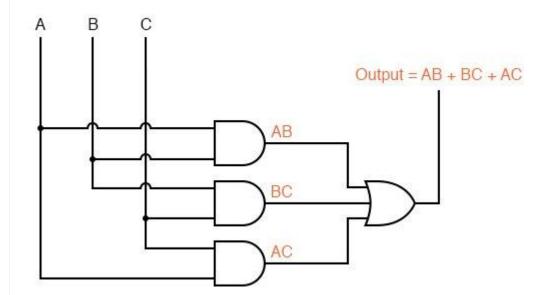

As a result of the simplification, we can now build much simpler logic circuits performing the same function:

Either one of these circuits will adequately perform the task of operating the incinerator waste valve based on a flame verification from two out of the three flame sensors.

At minimum, this is what we need to have a safe incinerator system.

We can, however, extend the functionality of the system by adding to it logic circuitry designed to detect if any one of the sensors does not agree with the other two.

If all three sensors are operating properly, they should detect flame with equal accuracy.

Thus, they should either all register "low" (000: no flame) or all register "high" (111: good flame).

Any other output combination (001, 010, 011, 100, 101, or 110) constitutes a disagreement between sensors, and may therefore serve as an indicator of a potential sensor failure.

If we added circuitry to detect any one of the six "sensor disagreement" conditions, we could use the output of that circuitry to activate an alarm.

Whoever is monitoring the incinerator would then exercise judgment in either continuing to operate with a possible failed sensor (inputs: 011, 101, or 110), or shut the incinerator down to be absolutely safe.

Also, if the incinerator is shut down (no flame), and one or more of the sensors still indicates flame (001, 010, 011, 100, 101, or 110) while the other(s) indicate(s) no flame, it will be known that a definite sensor problem exists.

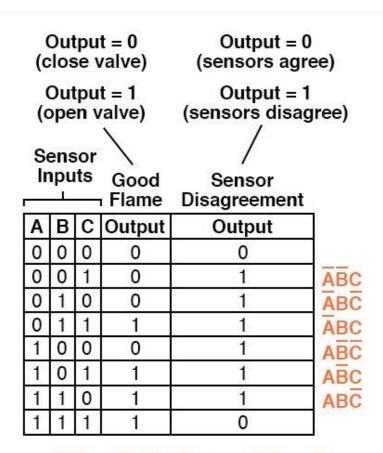

The first step in designing this "sensor disagreement" detection circuit is to write a truth table describing its behavior.

Since we already have a truth table describing the output of the "good flame" logic circuit, we can simply add another output column to the table to represent the second circuit, and make a table representing the entire logic system:

|        |     |       | t = 0<br>/alve) | Output = 0<br>(sensors agree)         |  |  |  |  |

|--------|-----|-------|-----------------|---------------------------------------|--|--|--|--|

|        |     |       | t = 1<br>valve) | Output = 1<br>(sensors disagree)<br>/ |  |  |  |  |

| 10,233 | ens | 0.000 | 1               | /                                     |  |  |  |  |

| Ir     | npu | Its   | Good            | Sensor                                |  |  |  |  |

| Г      | , S |       | Flame           | Disagreement                          |  |  |  |  |

| Α      | В   | С     | Output          | Output                                |  |  |  |  |

| 0      | 0   | 0     | 0               | 0                                     |  |  |  |  |

| 0      | 0   | 1     | 0               | 1                                     |  |  |  |  |

| 0      | 1   | 0     | 0               | 1                                     |  |  |  |  |

| 0      | 1   | 1     | 1               | 1                                     |  |  |  |  |

| 1      | 0   | 0     | 0               | 1                                     |  |  |  |  |

| 1      | 0   | 1     | 1               | 1                                     |  |  |  |  |

| 1      | 1   | 0     | 1               | 1                                     |  |  |  |  |

| 1      | 1   | 1     | 1               | 0                                     |  |  |  |  |

While it is possible to generate a Sum-Of-Products expression for this new truth table column, it would require six terms, of three variables each!

Such a Boolean expression would require many steps to simplify, with a large potential for making algebraic errors:

# $Output = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$

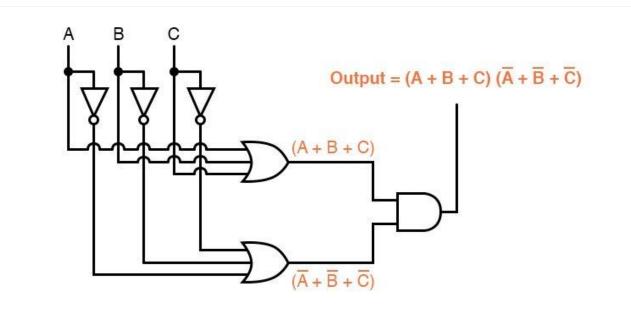

#### **Using Product-Of-Sums**

An alternative to generating a Sum-Of-Products expression to account for all the "high" (1) output conditions in the truth table is to generate a *Product-Of-Sums*, or *POS*, expression, to account for all the "low" (0) output conditions instead.

Being that there are much fewer instances of a "low" output in the last truth table column, the resulting Product-Of-Sums expression should contain fewer terms.

As its name suggests, a Product-Of-Sums expression is a set of added terms (*sums*), which are multiplied (*product*) together.

An example of a POS expression would be (A + B)(C + D), the product of the sums "A + B" and "C + D".

To begin, we identify which rows in the last truth table column have "low" (0) outputs, and write a Boolean sum term that would equal 0 for that row's input conditions.

For instance, in the first row of the truth table, where A=0, B=0, and C=0, the sum term would be (A + B + C), since that term would have a value of 0 if and only if A=0, B=0, and C=0:

|     |            |   | t = 0<br>/alve) | Output = 0<br>(sensors agre           |             |  |  |  |

|-----|------------|---|-----------------|---------------------------------------|-------------|--|--|--|

|     |            |   | t = 1<br>/alve) | Output = 1<br>(sensors disagree)<br>/ |             |  |  |  |

| 100 | ens<br>npu |   | Good<br>Flame   | /<br>Sensor<br>Disagreement           |             |  |  |  |

| Α   | В          | С | Output          | Output                                | ]           |  |  |  |

| 0   | 0          | 0 | 0               | 0                                     | (A + B + C) |  |  |  |

| 0   | 0          | 1 | 0               | 1                                     |             |  |  |  |

| 0   | 1          | 0 | 0               | 11                                    |             |  |  |  |

| 0   | 1          | 1 | 1               | 1                                     |             |  |  |  |

| 1   | 0          | 0 | 0               | 1                                     |             |  |  |  |

| 1   | 0          | 1 | 1               | 1                                     |             |  |  |  |

| 1   | 1          | 0 | 1               | 1                                     | ]           |  |  |  |

| 1   | 1          | 1 | 1               | 0                                     |             |  |  |  |

Only one other row in the last truth table column has a "low" (0) output, so all we need is one more sum term to complete our Product-Of-Sums expression.

This last sum term represents a 0 output for an input condition of A=1, B=1 and C=1.

Therefore, the term (Maxterm) must be written as (A' + B' + C'), because only the sum of the complemented input variables would equal 0 for that condition only:

| Output = 0<br>(close valve) |   |             |                         | Output = 0<br>(sensors agre                                 |                                                |

|-----------------------------|---|-------------|-------------------------|-------------------------------------------------------------|------------------------------------------------|

| (c<br>Se                    |   | en v<br>sor | t = 1<br>valve)<br>Good | Output = 1<br>(sensors disag<br>/<br>Sensor<br>Disagreement | iree)                                          |

| Α                           | В | С           | Output                  | Output                                                      |                                                |

| 0                           | 0 | 0           | 0                       | 0                                                           | (A + B + C)                                    |

| 0                           | 0 | 1           | 0                       | 1                                                           |                                                |

| 0                           | 1 | 0           | 0                       | 1                                                           |                                                |

| 0                           | 1 | 1           | 1                       | 1                                                           | 15<br>- 0                                      |

| 1                           | 0 | 0           | 0                       | 1                                                           |                                                |

| 1                           | 0 | 1           | 1                       | 1                                                           |                                                |

| 1                           | 1 | 0           | 1                       | 1                                                           |                                                |

| 1                           | 1 | 1           | 1                       | 0                                                           | $(\overline{A} + \overline{B} + \overline{C})$ |

The completed Product-Of-Sums expression, of course, is the multiplicative combination of these two sum Maxterms:

| Output = 0<br>(close valve)          |          |    |               | Output = 0<br>(sensors agree)    |                                                |  |  |

|--------------------------------------|----------|----|---------------|----------------------------------|------------------------------------------------|--|--|

| Output = 1<br>(open valve)<br>Sensor |          |    |               | Output = 1<br>(sensors disagree) |                                                |  |  |

| Ir                                   | ipu<br>I | ts | Good<br>Flame | Sensor<br>Disagreement           |                                                |  |  |

| Α                                    | В        | С  | Output        | Output                           |                                                |  |  |

| 0                                    | 0        | 0  | 0             | 0                                | (A + B + C)                                    |  |  |

| 0                                    | 0        | 1  | 0             | 1                                |                                                |  |  |

| 0                                    | 1        | 0  | 0             | 1                                |                                                |  |  |

| 0                                    | 1        | 1  | 1             | 1                                |                                                |  |  |

| 1                                    | 0        | 0  | 0             | 1                                |                                                |  |  |

| 1                                    | 0        | 1  | 1             | 1                                |                                                |  |  |

| 1                                    | 1        | 0  | 1             | 1                                |                                                |  |  |

| 4                                    | 1        | 1  | 1             | 0                                | $(\overline{A} + \overline{B} + \overline{C})$ |  |  |

Output =  $(A + B + C) (\overline{A} + \overline{B} + \overline{C})$

Whereas a Sum-Of-Products expression could be implemented in the form of a set of AND gates with their outputs connecting to a single OR gate, a Product-Of-Sums expression can be implemented as a set of OR gates feeding into a single AND gate:

As you can see, both the Sum-Of-Products and Products-Of-Sums standard Boolean forms are powerful tools when applied to truth tables.

They allow us to derive a Boolean expression—and ultimately, an actual logic circuit—from nothing but a truth table, which is a written specification for what we want a logic circuit to do.

To be able to go from a written specification to an actual circuit using simple, deterministic procedures means that it is possible to automate the design process for a digital circuit.

#### **REVIEW:**

• Sum-Of-Products, or SOP, Boolean expressions may be generated from truth tables quite easily, by determining which rows of the table have an output of 1, writing one product term for each row, and finally summing all the product terms. This creates a Boolean expression representing the truth table as a whole.

• Sum-Of-Products expressions lend themselves well to implementation as a set of AND gates (products) feeding into a single OR gate (sum).

• Product-Of-Sums, or POS, Boolean expressions may also be generated from truth tables quite easily, by determining which rows of the table have an output of 0, writing one sum term for each row, and finally multiplying all the sum terms. This creates a Boolean expression representing the truth table as a whole.

• Product-Of-Sums expressions lend themselves well to implementation as a set of OR gates (sums) feeding into a single AND gate (product).

#### Karnaugh Maps, Truth Tables, and Boolean Expressions

Maurice Karnaugh, a telecommunications engineer, developed the Karnaugh map at Bell Labs in 1953 while designing digital logic based telephone switching circuits.

#### The Use of Karnaugh Map

Karnaugh maps reduce logic functions more quickly and easily compared to Boolean algebra. By reduce we mean simplify, reducing the number of gates and inputs.

We like to simplify logic to a lowest cost form to save costs by elimination of components. We define lowest cost as being the lowest number of gates with the lowest number of inputs per gate.

Given a choice, most students do logic simplification with Karnaugh maps rather than Boolean algebra once they learn this tool.

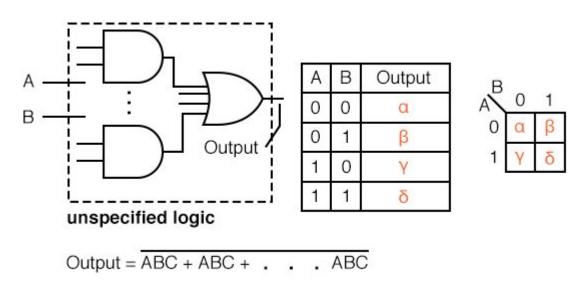

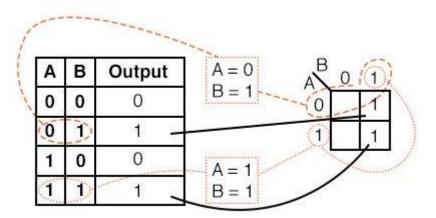

Two inputs A and B can take on values of either 0 or 1, high or low, open or closed, True or False, as the case may be. There are  $2^2 = 4$  combinations of inputs producing an output.

These outputs may be recorded in the truth table, or in the Karnaugh map. Look at the Karnaugh map as being a rearranged truth table.

The Output of the Boolean equation may be computed by the laws of Boolean algebra and transferred to the truth table or Karnaugh map.

| А | В | Output |   | /  | B  | 1   |   |

|---|---|--------|---|----|----|-----|---|

| 0 | 0 | α      | 1 | /  | AN | 10/ | 1 |

| 0 | 1 | β      | / | 91 | 0  | a   | β |

| 1 | 0 | Y      | 1 |    | 1  | _Y  | δ |

| 1 | 1 | δ      | Ē |    | _  | _   |   |

The outputs of a truth table correspond on a one-to-one basis to Karnaugh map entries. Starting at the top of the truth table, the A=0, B=0 inputs produce an output  $\alpha$ .

Note that this same output  $\alpha$  is found in the Karnaugh map at the A=0, B=0 cell address, upper left corner of K-map where the A=0 row and B=0 column intersect. The other truth table outputs  $\beta$ ,  $\chi$ ,  $\delta$  from inputs AB=01, 10, 11 are found at corresponding K-map locations.

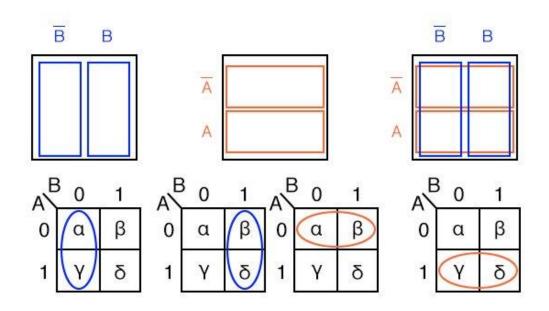

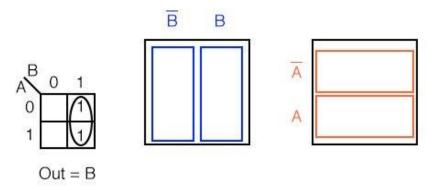

Below, we show the adjacent 2-cell regions in the 2-variable K-map like Boolean regions.

Cells  $\alpha$  and  $\chi$  are adjacent in the K-map as ellipses in the left most K-map below. Referring to the previous truth table, this is not the case. There is another truth table entry ( $\beta$ ) between them. Which brings us to the whole point of the organizing the K-map into a square array, cells with any Boolean variables in common need to be close to one another so as to present a pattern that jumps out at us. For cells  $\alpha$  and  $\chi$  they have the Boolean variable B' in common. We know this because B=0 (same as B') for the column above cells  $\alpha$  and  $\chi$ . Compare this to the square Venn diagram above the K-map.

A similar line of reasoning shows that  $\beta$  and  $\delta$  have Boolean B (B=1) in common. Then,  $\alpha$  and  $\beta$  have Boolean A' (A=0) in common. Finally,  $\chi$  and  $\delta$  have Boolean A (A=1) in common. Compare the last two maps to the middle square Venn diagram.

To summarize, we are looking for commonality of Boolean variables among cells. The Karnaugh map is organized so that we may see that commonality. Let's try some examples.

Examples

| Α | в | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

### Example:

Transfer the contents of the truth table to the Karnaugh map above.

### Solution:

The truth table contains two 1s. the K- map must have both of them. locate the first 1 in the 2nd row of the truth table above.

• note the truth table AB address

- locate the cell in the K-map having the same address

- place a 1 in that cell

Repeat the process for the 1 in the last line of the truth table.

# Example:

For the Karnaugh map in the above problem, write the Boolean expression. Solution is below.

# Solution:

Look for adjacent cells, that is, above or to the side of a cell. Diagonal cells are not adjacent. Adjacent cells will have one or more Boolean variables in common.

- Group (circle) the two 1s in the column

- Find the variable(s) top and/or side which are the same for the group, Write this as the Boolean result. It is B in our case.

• Ignore variable(s) which are not the same for a cell group. In our case A varies, is both 1 and 0, ignore Boolean A.

• Ignore any variable not associated with cells containing 1s. B' has no ones under it. Ignore B'

• Result Out = B

This might be easier to see by comparing to the Venn diagrams to the right, specifically the B column.

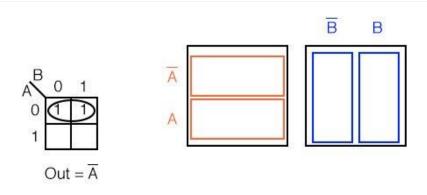

# Example:

Write the Boolean expression for the Karnaugh map below.

Solution: (above)

- Group (circle) the two 1's in the row

- Find the variable(s) which are the same for the group, Out = A'

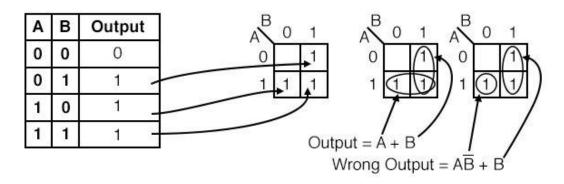

### Example:

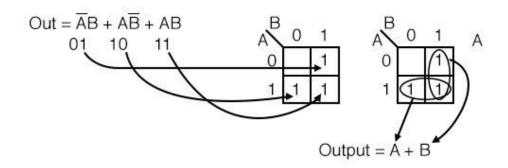

For the Truth table below, transfer the outputs to the Karnaugh, then write the Boolean expression for the result.

# Solution:

Transfer the 1s from the locations in the Truth table to the corresponding locations in the K-map.

- Group (circle) the two 1's in the column under B=1

- Group (circle) the two 1's in the row right of A=1

- Write product term for first group = B

- Write product term for second group = A

- Write Sum-Of-Products of above two terms Output = A+B

The solution of the K-map in the middle is the simplest or lowest cost solution. A less desirable solution is at far right. After grouping the two 1s, we make the mistake of forming a group of 1-cell. The reason that this is not desirable is that:

• The single cell has a product term of AB'

- The corresponding solution is Output = AB' + B

- This is not the simplest solution

The way to pick up this single 1 is to form a group of two with the 1 to the right of it as shown in the lower line of the middle K-map, even though this 1 has already been included in the column group (B). We are allowed to re-use cells in order to form larger groups. In fact, it is desirable because it leads to a simpler result.

We need to point out that either of the above solutions, Output or Wrong Output, are logically correct. Both circuits yield the same output. It is a matter of the former circuit being the lowest cost solution.

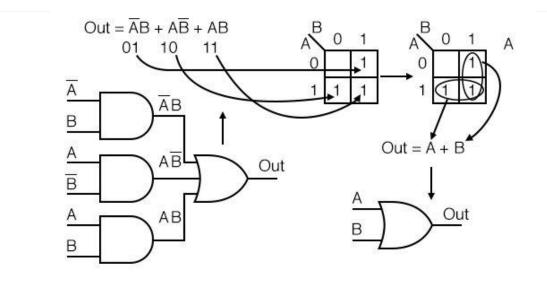

#### Example:

Fill in the Karnaugh map for the Boolean expression below, then write the Boolean expression for the result.

#### Solution: (above)

The Boolean expression has three product terms. There will be a 1 entered for each product term. Though, in general, the number of 1s per product term varies with the number of variables in the product term compared to the size of the K-map.

The product term is the address of the cell where the 1 is entered. The first product term, A'B, corresponds to the 01 cell in the map. A 1 is entered in this cell. The other two P-terms are entered for a total of three 1s

Next, proceed with grouping and extracting the simplified result as in the previous truth table problem.

# Example:

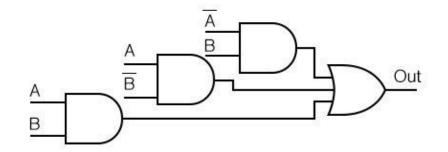

Simplify the logic diagram below.

**Solution:** (Figure below)

• Write the Boolean expression for the original logic diagram as shown

below

- Transfer the product terms to the Karnaugh map

- Form groups of cells as in previous examples

- Write Boolean expression for groups as in previous examples

- Draw simplified logic diagram

**Example**: Simplify the logic diagram below.

### Solution:

• Write the Boolean expression for the original logic diagram shown above

- Transfer the product terms to the Karnaugh map.

- It is not possible to form groups.

- No simplification is possible; leave it as it is.

No logic simplification is possible for the above diagram. This sometimes happens. Neither the methods of Karnaugh maps nor Boolean algebra can simplify this logic further.

We show an Exclusive-OR schematic symbol above; however, this is not a logical simplification. It just makes a schematic diagram look nicer.

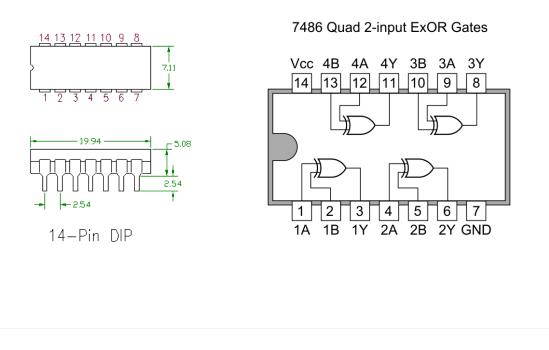

Since it is not possible to simplify the Exclusive-OR logic and it is widely used, it is provided by manufacturers as a basic integrated circuit (7486).

### Logic Simplification With Karnaugh Maps

The logic simplification examples that we have done so far could have been performed with Boolean algebra about as quickly. Real world logic simplification problems call for larger Karnaugh maps so that we may do serious work.

We will work some contrived examples below. By contrived, we mean examples which illustrate techniques.

This approach will develop the tools we need to transition to the more complex applications.

#### Karnaugh Maps and Gray Code Sequence

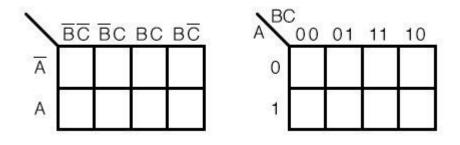

We show our previously developed Karnaugh map. We will use the form on the right.

Note the sequence of numbers across the top of the map. It is not in binary sequence which would be **00, 01, 10, 11**. It is **00, 01, 11 10**, which is Gray code sequence. Gray code sequence only changes one binary bit as we go from one number to the next in the sequence, unlike binary.

That means that adjacent cells will only vary by one bit, or Boolean variable. This is what we need to organize the outputs of a logic function so that we may view commonality.

Moreover, the column and row headings must be in Gray code order, or the map will not work as a Karnaugh map. Cells sharing common Boolean variables would no longer be adjacent, nor show visual patterns. Adjacent cells vary by only one bit because a Gray code sequence varies by only one bit.

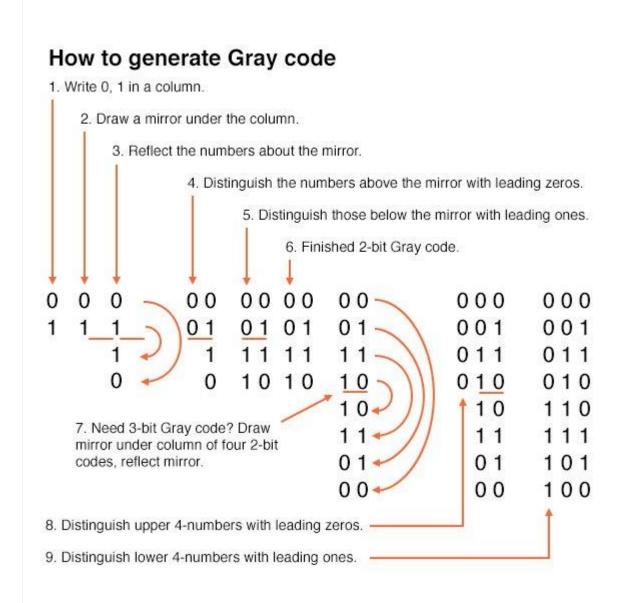

### **Generating Gray Code**

If we sketch our own Karnaugh maps, we need to generate Gray code for any size map that we may use. This is how we generate <u>Gray code</u> of any size.

Note that the Gray code sequence, above right, only varies by one bit as we go down the list, or bottom to top up the list. This property of Gray code is often useful for digital electronics in general. In particular, it is applicable to Karnaugh maps.

### **Examples of Simplification with Karnaugh Maps**

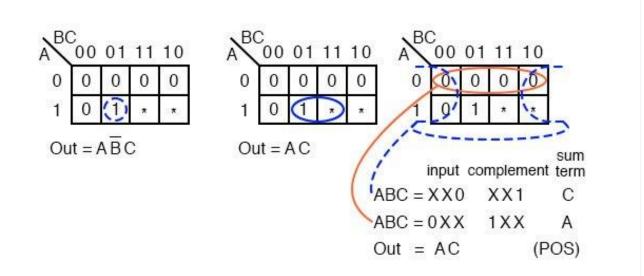

Let us move on to some examples of simplification with 3-variable Karnaugh maps. We show how to map the product terms of the unsimplified logic to the K-map.

We illustrate how to identify groups of adjacent cells which leads to a Sum-of-Products simplification of the digital logic.

Out =

$$\overline{A} \overline{B} \overline{C} + \overline{A} \overline{B} C$$

$A 00 01 11 10$

$0 1 1$

$1 0$

Out =  $\overline{A} \overline{B}$

Above we, place the 1's in the K-map for each of the product terms, identify a group of two, then write a *p-term* (product term) for the sole group as our simplified result.

Out =

$$\overline{A}\overline{B}\overline{C} + \overline{A}\overline{B}C + \overline{A}BC + \overline{A}BC + \overline{A}B\overline{C}$$

$A 00 01 11 10$

$0 1 1 1 1$

$1 1 1$

Out =  $\overline{A}$

Mapping the four product terms above yields a group of four covered by Boolean A'

Mapping the four p-terms yields a group of four, which is covered by one variable C.

Out =

$$\overline{A}\overline{B}\overline{C} + \overline{A}\overline{B}C + \overline{A}BC + \overline{A}B\overline{C} + ABC + AB\overline{C}$$

$A \xrightarrow{BC} 00 \ 01 \ 11 \ 10$

$0 \ 1 \ 1 \ 1 \ 1$

Out =  $\overline{A} + B$

After mapping the six p-terms above, identify the upper group of four, pick up the lower two cells as a group of four by sharing the two with two more from the other group. Covering these two with a group of four gives a simpler result.

Since there are two groups, there will be two p-terms in the Sum-of-Products result  $\mathbf{A'+B}$

Out =  $\overline{A}BC + ABC$  A 00 01 11 10 0 1 1Out = BC The two product terms above form one group of two and simplifies to BC

Mapping the four p-terms yields a single group of four, which is **B**

Mapping the four p-terms above yields a group of four. Visualize the group of four by rolling up the ends of the map to form a cylinder, then the cells are adjacent. We normally mark the group of four as above left.

Out of the variables A, B, C, there is a common variable: C'. C' is a 0 overall four cells. The final result is C'

The six cells above from the unsimplified equation can be organized into two groups of four. These two groups should give us two p-terms in our simplified result of  $\mathbf{A}^* + \mathbf{C}^*$ .

# Simplifying Boolean Equations with Karnaugh Maps

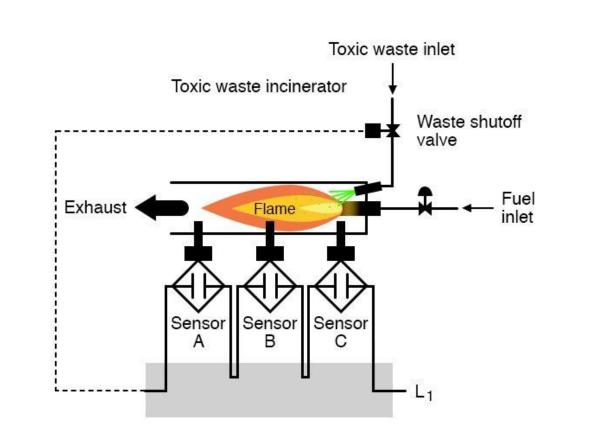

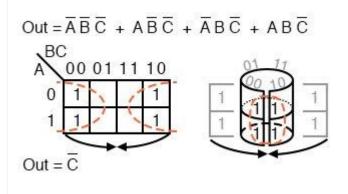

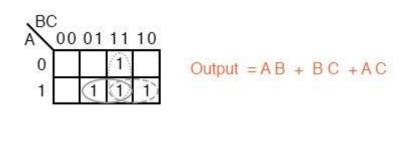

Below, we revisit the <u>toxic waste incinerator</u> from the Boolean algebra chapter. See Boolean algebra chapter for details on this example. We will simplify the logic using a Karnaugh map.

The Boolean equation for the output has four product terms. Map four 1's corresponding to the p-terms. Forming groups of cells, we have three groups of two. There will be three p-terms in the simplified result, one for each group. See <u>Converting Truth Tables into Boolean Expressions</u> from chapter 7 for a gate diagram of the result, which is reproduced below.

Below we repeat the Boolean algebra simplification of the toxic waste incinerator for comparison.

This case illustrates why the Karnaugh map is widely used for logic simplification.

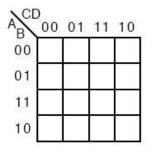

### Larger 4-variable Karnaugh Maps

Knowing how to generate Gray code should allow us to build larger maps. Actually, all we need to do is look at the left to right sequence across the top of the 3variable map, and copy it down the left side of the 4-variable map. See below.

#### **Reductions of 4 Variable K Maps**

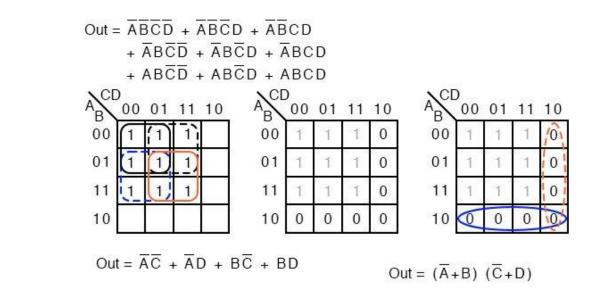

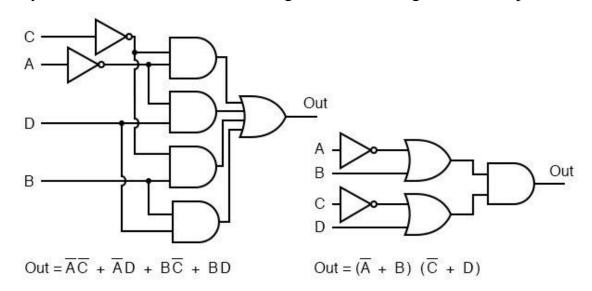

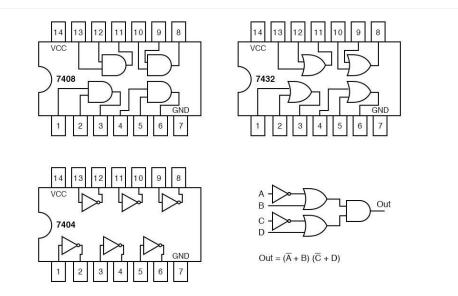

The following four variable Karnaugh maps illustrate the reduction of Boolean expressions too tedious for Boolean algebra. Reductions could be done with Boolean algebra.

However, the Karnaugh map is faster and easier, especially if there are many logic reductions to do.

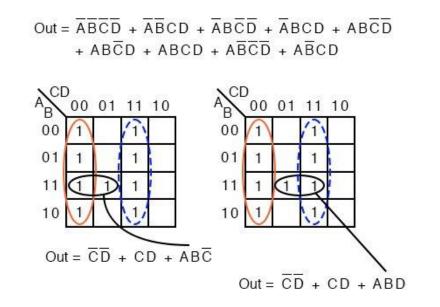

Out =  $\overline{ABCD} + \overline{ABCD} + ABCD + AB$

The above Boolean expression has seven product terms. They are mapped top to bottom and left to right on the K-map above. For example, the first P-term A'B'CD is the first row, 3rd cell, corresponding to map location A=0, B=0, C=1, D=1.

The other product terms are placed in a similar manner. Encircling the largest groups possible, two groups of four are shown above.

The dashed horizontal group corresponds to the simplified product term AB. The vertical group corresponds to Boolean CD. Since there are two groups, there will be two product terms in the Sum-Of-Products result of **Out=AB+CD**.

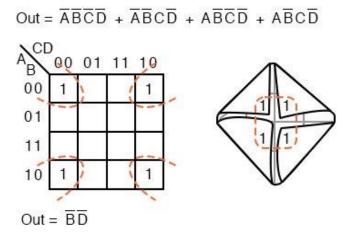

Fold up the corners of the map below like it is a napkin to make the four cells physically adjacent.

The four cells above are a group of four because they all have the Boolean variables **B**' and **D**' in common. In other words, **B=0** for the four cells, and **D=0** for the four cells.

The other variables (A, C) are 0 in some cases, 1 in other cases with respect to the four corner cells.

Thus, these variables (A, C) are not involved with this group of four. This single group comes out of the map as one product term for the simplified result: **Out=B'D'**

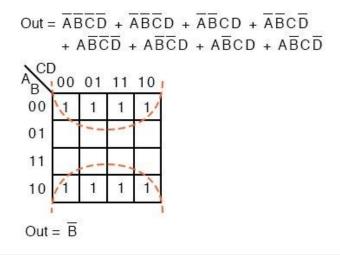

For the K-map below, roll the top and bottom edges into a cylinder forming eight adjacent cells.

The above group of eight has one Boolean variable in common: B=0. Therefore, the one group of eight is covered by one p-term: **B'**. The original eight-term Boolean expression simplifies to **Out=B'**

#### **P-Terms in 4 Variable K Maps**

The Boolean expression below has nine p-terms, three of which have three Booleans instead of four. The difference is that while four Boolean variable product terms cover one cell, the three Boolean p-terms cover a pair of cells each.

The six product terms of four Boolean variables map in the usual manner above as single cells. The three Boolean variable terms (three each) map as cell pairs, which is shown above.

Note that we are mapping p-terms into the K-map, not pulling them out at this point.

For the simplification, we form two groups of eight. Cells in the corners are shared with both groups. This is fine. In fact, this leads to a better solution than forming a group of eight and a group of four without sharing any cells. Final Solution

### is Out=B'+D'

Below we map the unsimplified Boolean expression to the Karnaugh map.

Above, three of the cells form into groups of two cells. A fourth cell cannot be combined with anything, which often happens in "real world" problems. In this case, the Boolean p-term **ABCD** is unchanged in the simplification process. Result: **Out=**

### B'C'D'+A'B'D'+ABCD

Often times there is more than one minimum cost solution to a simplification problem. Such is the case illustrated below.

Both results above have four product terms of three Boolean variable each. Both are equally valid *minimal* cost solutions. The difference in the final solution is due to how the cells are grouped as shown above.

A minimal cost solution is a valid logic design with the minimum number of gates with the minimum number of inputs.

Below we map the unsimplified Boolean equation as usual and form a group of four as a first simplification step. It may not be obvious how to pick up the remaining cells.

Pick up three more cells in a group of four, center above. There are still two cells remaining. the minimal cost method to pick up those is to group them with neighboring cells as groups of four as at above right.

On a cautionary note, do not attempt to form groups of three. Groupings must be powers of 2, that is, 1, 2, 4, 8 ...

Below we have another example of two possible minimal cost solutions. Start by forming a couple of groups of four after mapping the cells.

The two solutions depend on whether the single remaining cell is grouped with the first or the second group of four as a group of two cells. That cell either comes out as either **ABC'** or **ABD**, your choice.

Either way, this cell is covered by either Boolean product term. Final results are shown above.

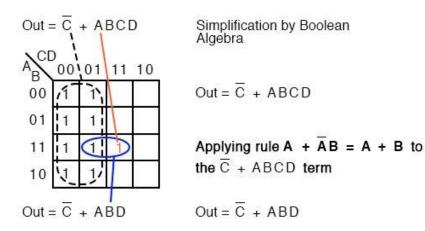

Below we have an example of a simplification using the Karnaugh map at left or Boolean algebra at right. Plot  $\mathbb{C}$  on the map as the area of all cells covered by address  $\mathbb{C}=0$ , the 8-cells on the left of the map. Then, plot the single **ABCD** cell.

That single cell forms a group of 2-cell as shown, which simplifies to P-term **ABD**, for an end result of **Out** = C' + ABD.

This (above) is a rare example of a four-variable problem that can be reduced with Boolean algebra without a lot of work, assuming that you remember the theorems.

#### **Minterm and Maxterm Solution**

So far we have been finding Sum-Of-Product (SOP) solutions to logic reduction problems. For each of these SOP solutions, there is also a Product-Of-Sums solution (POS), which could be more useful, depending on the application.

Before working a Product-Of-Sums solution, we need to introduce some new terminology. We just want to establish a formal procedure for minterms for comparison to the new procedure for maxterms.

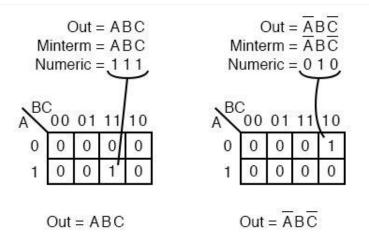

#### Minterm

A *minterm* is a Boolean expression resulting in **1** for the output of a single cell, and **0**s for all other cells in a Karnaugh map, or truth table. If a minterm has a single **1** and the remaining cells as **0**s, it would appear to cover a minimum area of **1**s.

The illustration above left shows the minterm **ABC**, a single product term, as a single **1** in a map that is otherwise **0**s. We have not shown the **0**s in our Karnaugh maps up to this point, as it is customary to omit them unless specifically needed. Another minterm **A'BC'** is shown above right.

The point to review is that the address of the cell corresponds directly to the minterm being mapped. That is, the cell **111** corresponds to the minterm **ABC** above left.

Above right we see that the minterm **A'BC'** corresponds directly to the cell **010**. A Boolean expression or map may have multiple minterms.

Referring to the above figure, Let's summarize the procedure for placing a minterm in a K-map:

- Identify the minterm (product term) term to be mapped.

- Write the corresponding binary numeric value.

- Use binary value as an address to place a 1 in the K-map

- Repeat steps for other minterms (P-terms within a Sum-Of-Products).

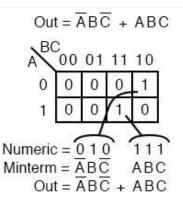

A Boolean expression will more often than not consist of multiple minterms corresponding to multiple cells in a Karnaugh map as shown above. The multiple minterms in this map are the individual minterms which we examined in the previous figure above.

The point we review for reference is that the **1**s come out of the K-map as a binary cell address which converts directly to one or more product terms.

By directly we mean that a **0** corresponds to a complemented variable, and a **1** corresponds to a true variable. Example: **010** converts directly to **A'BC'**.

There was no reduction in this example. Though, we do have a Sum-Of-Products result from the minterms.

Referring to the above figure, Let's summarize the procedure for writing the Sum-Of-Products reduced Boolean equation from a K-map:

• Form largest groups of **1**s possible covering all minterms. Groups must be a power of 2.

- Write binary numeric value for groups.

- Convert binary value to a product term.

• Repeat steps for other groups. Each group yields a p-terms within a Sum-Of-Products.

Nothing new so far, a formal procedure has been written down for dealing with minterms. This serves as a pattern for dealing with maxterms.

Next we check the Boolean function which is 0 for a single cell and 1s for all others.

#### Maxterm

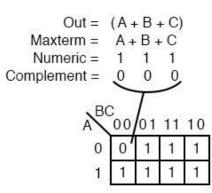

A *maxterm* is a Boolean expression resulting in a **0** for the output of a single cell expression, and **1**s for all other cells in the Karnaugh map, or truth table. The illustration above left shows the maxterm (A+B+C), a single sum term, as a single **0** in a map that is otherwise **1**s.

If a maxterm has a single **0** and the remaining cells as **1**s, it would appear to cover a maximum area of **1**s.

There are some differences now that we are dealing with something new, maxterms. The maxterm is a  $\mathbf{0}$ , not a  $\mathbf{1}$  in the Karnaugh map. A maxterm is a sum term,  $(\mathbf{A}+\mathbf{B}+\mathbf{C})$  in our example, not a product term. It also looks strange that  $(\mathbf{A}+\mathbf{B}+\mathbf{C})$  is mapped into the cell **000**.

For the equation Out=(A+B+C)=0, all three variables (A, B, C) must individually be equal to 0. Only (0+0+0)=0 will equal 0. Thus we place our sole 0 for minterm (A+B+C) in cell A,B,C=000 in the K-map, where the inputs are all 0.

This is the only case which will give us a **0** for our maxterm. All other cells contain **1**s because any input values other than ((0,0,0) for (A+B+C) yields **1**s upon evaluation.

Referring to the above figure, the procedure for placing a maxterm in the K-map is:

- Identify the Sum term to be mapped.

- Write corresponding binary numeric value.

- Form the complement

- Use the complement as an address to place a **0** in the K-map

- Repeat for other maxterms (Sum terms within Product-of-Sums expression).

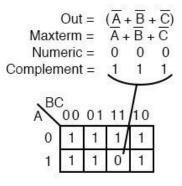

Another maxterm A'+B'+C' is shown above. Numeric 000 corresponds to A'+B'+C'. The complement is 111. Place a 0 for maxterm (A'+B'+C') in this cell (1,1,1) of the K-map as shown above.

Why should (A'+B'+C') cause a 0 to be in cell 111? When A'+B'+C' is (1'+1'+1'), all 1s in, which is (0+0+0) after taking complements, we have the only condition that will give us a 0. All the 1s are complemented to all 0s, which is 0 when ORed.

A Boolean Product-Of-Sums expression or map may have multiple maxterms as shown above. Maxterm (A+B+C) yields numeric **111** which complements to **000**, placing a **0** in cell (**0**,**0**,**0**). Maxterm (A+B+C') yields numeric **110** which complements to **001**, placing a **0** in cell (**0**,**0**,**1**).

Now that we have the k-map setup, what we are really interested in is showing how to write a Product-Of-Sums reduction. Form the **0**s into groups. That would be a

group of two below. Write the binary value corresponding to the sum-term which is (0,0,X).

Both A and B are **0** for the group. But, **C** is both **0** and **1** so we write an **X** as a place holder for **C**. Form the complement (1,1,X). Write the Sumterm (A+B) discarding the **C** and the **X** which held its' place.

In general, expect to have more sum-terms multiplied together in the Product-Of-Sums result. Though, we have a simple example here.

Out =

$$(A + B + C) (A + B + \overline{C})$$

A B C =  $0 \ 0 \ x$

Complement =  $1 \ 1 \ x$

Sum-term =  $(A + B)$

Out =  $(A + B)$

Let's summarize the procedure for writing the Product-Of-Sums Boolean reduction for a K-map:

• Form largest groups of 0s possible, covering all maxterms. Groups must be a power of 2.

- Write binary numeric value for group.

- Complement binary numeric value for group.

- Convert complement value to a sum-term.

- Repeat steps for other groups. Each group yields a sum-term within a Product-

Of-Sums result.

# Examples

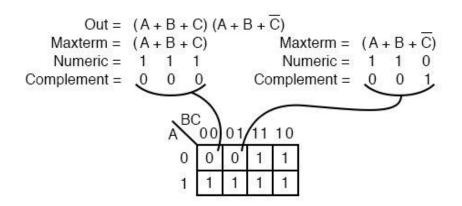

### **Example:**

Simplify the Product-Of-Sums Boolean expression below, providing a result in POS form.

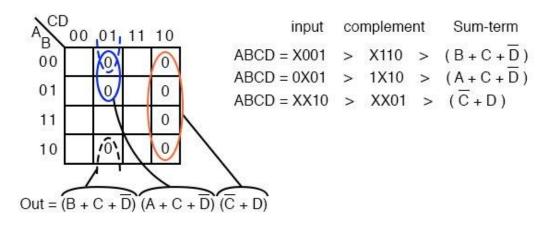

Out=  $(A+B+C+\overline{D})(A+B+\overline{C}+D)(A+\overline{B}+C+\overline{D})(A+\overline{B}+\overline{C}+D)$  $(\overline{A}+\overline{B}+\overline{C}+D)(\overline{A}+B+C+\overline{D})(\overline{A}+B+\overline{C}+D)$

#### Solution:

Transfer the seven maxterms to the map below as 0s. Be sure to complement the input variables in finding the proper cell location.

We map the **0**s as they appear left to right top to bottom on the map above. We locate the last three maxterms with leader lines..

Once the cells are in place above, form groups of cells as shown below. Larger groups will give a sum-term with fewer inputs. Fewer groups will yield fewer sum-terms in the result.

We have three groups, so we expect to have three sum-terms in our POS result above. The group of 4-cells yields a 2-variable sum-term. The two groups of 2-cells give us two 3-variable sum-terms.

Details are shown for how we arrived at the Sum-terms above. For a group, write the binary group input address, then complement it, converting that to the Boolean sum-term. The final result is product of the three sums.

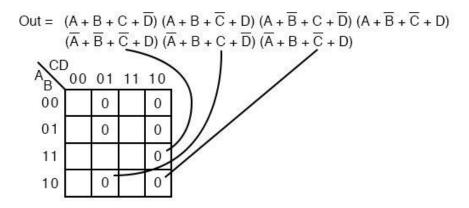

### Example:

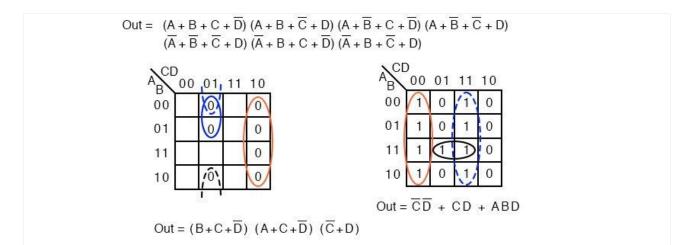

Simplify the Product-Of-Sums Boolean expression below, providing a result in SOP form.

$$\begin{array}{rl} \text{Out} = & (A + B + C + \overline{D}) \ (A + B + \overline{C} + D) \ (A + \overline{B} + C + \overline{D}) \ (A + \overline{B} + \overline{C} + D) \\ & (\overline{A} + \overline{B} + \overline{C} + D) \ (\overline{A} + B + C + \overline{D}) \ (\overline{A} + B + \overline{C} + D) \end{array}$$

### Solution:

This looks like a repeat of the last problem. It is except that we ask for a Sum-Of-Products Solution instead of the Product-Of-Sums which we just finished. Map the maxterm  $\mathbf{0}$ s from the Product-Of-Sums given as in the previous problem, below left.

Out =

$$(A + B + C + \overline{D}) (A + B + \overline{C} + D) (A + \overline{B} + C + \overline{D}) (A + \overline{B} + \overline{C} + D)$$

$(\overline{A} + \overline{B} + \overline{C} + D) (\overline{A} + B + C + \overline{D}) (\overline{A} + B + \overline{C} + D)$

| ACD 0 | 0 01 1            | 1 10 | ABCD |   | 01 | 11 | 10 |

|-------|-------------------|------|------|---|----|----|----|

| 00    | 0                 | 0    | 00   | 1 | 0  | 1  | 0  |

| 01    | 0                 | 0    | 01   | 1 | 0  | 1  | 0  |

| 11    | - 63 50 - 63 50 - | 0    | 11   | 1 | 1  | 1  | 0  |

| 10    | 0                 | 0    | 10   | 1 | 0  | 1  | 0  |

Then fill in the implied 1s in the remaining cells of the map above right.

| A  |   | 01 | 11 | 10 |

|----|---|----|----|----|

| 00 |   | 0  | 1  | 0  |

| 01 | 1 | 0  | 1  | 0  |

| 11 | 1 | T  | P  | 0  |

| 10 | 1 | 0  | 1  | 0  |

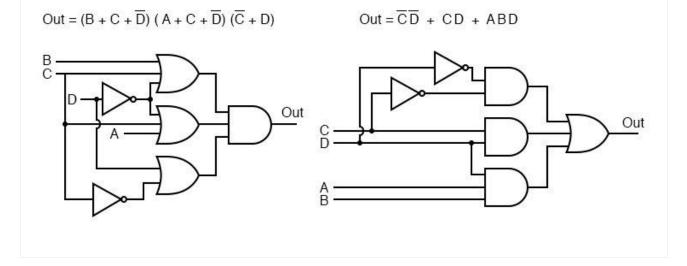

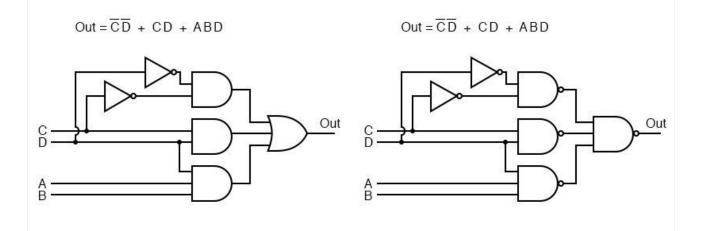

$Out = \overline{C}\overline{D} + CD + ABD$

Form groups of **1**s to cover all **1**s. Then write the Sum-Of-Products simplified result as in the previous section of this chapter. This is identical to a previous problem.

Above we show both the Product-Of-Sums solution, from the previous example, and the Sum-Of-Products solution from the current problem for comparison.